智能變電站的穩定運行靠什么來保障?

智能變電站的二次系統通常包含電子式互感器、合并單元、交換機、保護測控等設備。這些裝置必須基于統一的時間基準運行,這對智能變電站的時鐘同步系統提出嚴格的要求。智能變電站微秒級的對時系統究竟是如何實現的呢?

時間是基本物理量,那么時間也就會有精度的問題,不同時間源有著不同的精度。如AppleWatch與iPhone配合使用,同UTC時間誤差不超過50ms。50ms誤差對于人類的感知可以忽略,可是如果用在智能變電站中就顯得不盡人意了。

智能變電站的二次系統通常包含電子式互感器、合并單元、交換機、保護測控等設備。這些裝置必須基于統一的時間基準運行,方能滿足事件順序記錄(SOE)、故障錄波、實時數據采集時間一致性的要求,確保線路故障測距、相量和攻角動態監測、機組和電網參數校驗的準確性。這些要求對智能變電站的時鐘同步系統提出嚴格的要求。

IEC61850標準將變電站分為站空層、間隔層和過程層,對時間同步精度的要求,各層設備是不同的。間隔層設備需要到達ms精度;而過程層設備,由于主要傳輸采樣值、跳閘信息,需要達到μs的同步精度。智能變電站的測試設備DT6000系列(DT6000、DT6000E和DT6000S)的對時精度可達μs的同步精度,完全滿足變電站各層的設備的對時精度。

DT6000系列的對時系統

圖1.1DT6000系列的對時

DT6000系列的對時支持IRIG-B、PPS和IEEE1588三種對時,如圖1.1所示。三種協議全部采用FPGA硬解碼,解碼之后轉換為UTC時標,提供時間給SMV、GOOSE等其他協議,如SMV和GOOSE的接收的時標為硬時標,由FPGA進行打時標,將時間信息插入報文中,實時保存報文信息和時間。在對時的同時,FPGA還進行了校時,即將本地晶振引起的誤差(μs級)進行校正,動態調整均勻調節誤差值。

一、對時

1.PPS對時

檢測PPS正常與否,有兩個重要的判別依據:

(1)相鄰脈沖上升沿的時間間隔為1s。當相鄰脈沖上升沿的間隔時間與理想間隔時間(1s)相差大于10μs時,則判定輸入異常。

(2)脈沖寬度大于10μs,間隔大于500ms。當測量到的脈沖寬度小于10μs,或者測量到的脈沖間隔小于500ms時,則認為輸入異常。

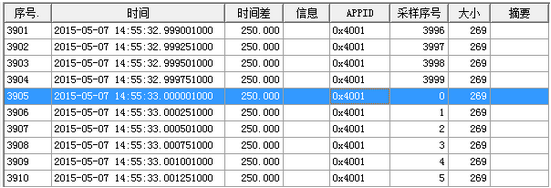

DT6000系列根據上述兩個判別依據并將輸入的信號進行了過濾,去除毛刺信號。如圖1.2所示為DT6000E經過PPS對時之后,SMV采樣計數器在整秒清零。

圖1.2整秒SMV采樣計數器清零

2.IRIG-B對時

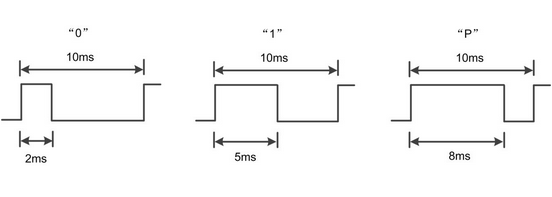

IRIG-B碼的幀周期是1s,包含100個碼元,每個碼元周期為10ms,即IRIG-B碼的碼元速率為100pps。IRIG-B碼有3種碼元,二進制“0”、“1”和位置識別標志Px,脈寬分別為2ms、5ms和8ms。脈沖信號如圖1.3所示。

圖1.3IRIG-B碼元圖

連續2個“P”碼元表示整秒的開始,第2個“P”碼元的脈沖前沿是“準時”參考點,定義其為“Pr”,后面攜帶當前的時間和時間控制相關的信息。IRIG-B的整秒“準時”參考點,SMV的采樣計數器的需要清零,這點和PPS是一樣的,如圖1.2所示。

如圖1.4所示為DT6000E的IRIG-B對時。

圖1.4IRIG-B對時

3.IEEE1588對時

IEEE1588報文的解碼和打時標都是在FPGA中進行的,工作在Slave模式。打時標是指在同步報文進入或者離開協議棧的時候,用本地時鐘信息標記同步報文的過程。時間戳的獲取方式直接影響時鐘同步的精度,獲取時間戳的地點約接近物理層,越能很好的避開報文在協議棧中的延時抖動,所能夠達到的同步精度也就越高。在FPGA中進行報文解碼和打時標為在MII層打時標,為硬件打時標,精度最高。

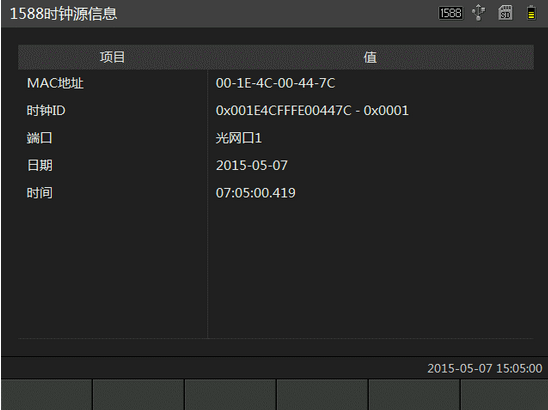

如圖1.5所示為DT6000E的IEEE1588對時。

圖1.5IEEE1588對時

二、校時

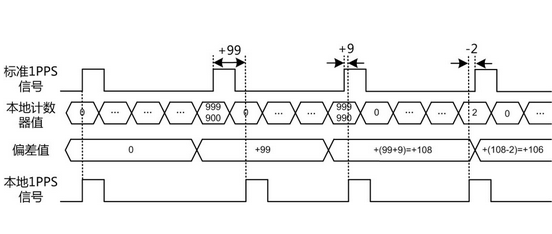

DT6000系列在對時的同時會進行校時,校正本地晶振的誤差值。圖1.6為校時調整的一個實例說明圖,由圖中可以看出第一次粗略調節值為+99,第二次精確調節為正向,此時的Value=+99+9=+108,第三次精確調節為反向,此時的Value=+108-2=+106,在獲取Value值的同時計數器也在一直均勻的調節。

圖1.6校時實例說明圖

校時電路(FPGA)工作在100MHz主頻下,經過實際測量,校正穩定之后,溫度變化不大的環境下,其精度誤差不超過20個周期(10ns),經過校時之后,對時精度從μs級可變為200ns級。并且采用校時電路之后,在移除校時設備之后都能長時間保持本地的時間的高準確度。

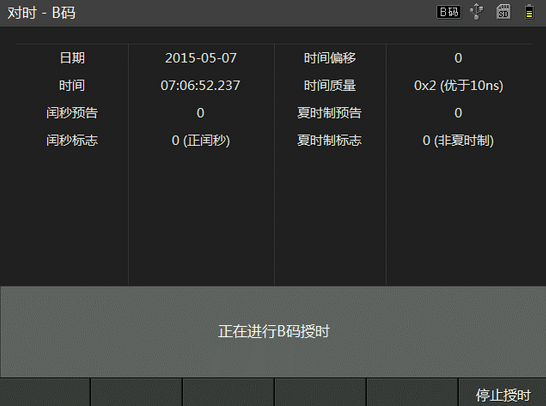

三、授時

DT6000系列支持IRIG-B碼和PPS的授時,DT6000S有兩個光串口,因此支持兩個光串口同時授時。如圖1.7所示為DT6000E的IRIG-B碼授時界面,PPS的授時等同。

圖1.7IRIG-B碼授時

責任編輯:電朵云